# VIPA System SLIO

FM | 050-1BA00 | Manual

HB300 | FM | 050-1BA00 | en | 19-38

Counter module advanced 1x32Bit - FM 050

VIPA GmbH Ohmstr. 4 91074 Herzogenaurach

Telephone: 09132-744-0 Fax: 09132-744-1864 Email: info@vipa.com Internet: www.vipa.com

# **Table of contents**

| 1 | General                          | . 4 |

|---|----------------------------------|-----|

|   | 1.1 Copyright © VIPA GmbH        | 4   |

|   | 1.2 About this manual            | 5   |

|   | 1.3 Safety information           | 6   |

| 2 | Basics and mounting              | . 7 |

|   | 2.1 Safety information for users | 7   |

|   | 2.2 System conception            |     |

|   | 2.2.1 Overview                   | 8   |

|   | 2.2.2 Components                 | 9   |

|   | 2.2.3 Accessories                | 11  |

|   | 2.2.4 Hardware revision          | 12  |

|   | 2.3 Dimensions                   | 12  |

|   | 2.4 Mounting periphery modules   | 15  |

|   | 2.5 Wiring periphery modules     | 18  |

|   | 2.6 Wiring power modules         | 20  |

|   | 2.7 Demounting periphery modules | 24  |

|   | 2.7.1 Easy Maintenance           |     |

|   | 2.8 Trouble shooting - LEDs      |     |

|   | 2.9 Installation guidelines      | 28  |

|   | 2.10 General data                | 30  |

| 3 | Hardware description             | 32  |

|   | 3.1 Properties                   | 32  |

|   | 3.2 Structure                    | 32  |

|   | 3.3 Technical data               | 35  |

| 4 | Deployment                       | 38  |

|   | 4.1 Fast introduction            | 38  |

|   | 4.2 In-/Output area              |     |

|   | 4.2.1 Input area 12byte          |     |

|   | 4.2.2 Output area 10byte         |     |

|   | 4.3 Parameter data               |     |

|   | 4.4 Counter - Functions          |     |

|   | 4.5 Counter additional functions |     |

|   | 4.6 Diagnostic and interrupt     | 58  |

|   |                                  |     |

General VIPA System SLIO

Copyright © VIPA GmbH

## 1 General

## 1.1 Copyright © VIPA GmbH

#### **All Rights Reserved**

This document contains proprietary information of VIPA and is not to be disclosed or used except in accordance with applicable agreements.

This material is protected by the copyright laws. It may not be reproduced, distributed, or altered in any fashion by any entity (either internal or external to VIPA), except in accordance with applicable agreements, contracts or licensing, without the express written consent of VIPA and the business management owner of the material.

For permission to reproduce or distribute, please contact: VIPA, Gesellschaft für Visualisierung und Prozessautomatisierung mbH Ohmstraße 4, D-91074 Herzogenaurach, Germany

Tel.: +49 9132 744 -0 Fax.: +49 9132 744-1864

EMail: info@vipa.de http://www.vipa.com

Every effort has been made to ensure that the information contained in this document was complete and accurate at the time of publishing. Nevertheless, the authors retain the right to modify the information.

This customer document describes all the hardware units and functions known at the present time. Descriptions may be included for units which are not present at the customer site. The exact scope of delivery is described in the respective purchase contract.

#### **EC Conformity Declaration**

Hereby, VIPA GmbH declares that the products and systems are in compliance with the essential requirements and other relevant provisions. Conformity is indicated by the CE marking affixed to the product.

## **Conformity Information**

For more information regarding CE marking and Declaration of Conformity (DoC), please contact your local VIPA customer service organization.

#### **Trademarks**

VIPA, SLIO, System 100V, System 200V, System 300V, System 300S, System 400V, System 500S and Commander Compact are registered trademarks of VIPA Gesellschaft für Visualisierung und Prozessautomatisierung mbH.

SPEED7 is a registered trademark of profichip GmbH.

SIMATIC, STEP, SINEC, TIA Portal, S7-300, S7-400 and S7-1500 are registered trademarks of Siemens AG.

Microsoft and Windows are registered trademarks of Microsoft Inc., USA.

Portable Document Format (PDF) and Postscript are registered trademarks of Adobe Systems, Inc.

All other trademarks, logos and service or product marks specified herein are owned by their respective companies.

VIPA System SLIO General

About this manual

# Information product support

Contact your local VIPA Customer Service Organization representative if you wish to report errors or questions regarding the contents of this document. If you are unable to locate a customer service centre, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telefax: +49 9132 744-1204

EMail: documentation@vipa.de

#### **Technical support**

Contact your local VIPA Customer Service Organization representative if you encounter problems with the product or have questions regarding the product. If you are unable to locate a customer service centre, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Tel.: +49 9132 744-1150 (Hotline)

EMail: support@vipa.de

#### 1.2 About this manual

#### Objective and contents

This manual describes the FM 050-1BA00 of the System SLIO from VIPA. It contains a description of the construction, project implementation and usage.

| Product | Order number | as of state:<br>HW |

|---------|--------------|--------------------|

| FM 050  | 050-1BA00    | 01                 |

#### **Target audience**

The manual is targeted at users who have a background in automation technology.

#### Structure of the manual

The manual consists of chapters. Every chapter provides a self-contained description of a specific topic.

#### Guide to the document

The following guides are available in the manual:

- An overall table of contents at the beginning of the manual

- References with page numbers

#### **Availability**

The manual is available in:

- printed form, on paper

- in electronic form as PDF-file (Adobe Acrobat Reader)

#### **Icons Headings**

Important passages in the text are highlighted by following icons and headings:

#### **DANGER!**

Immediate or likely danger. Personal injury is possible.

General VIPA System SLIO

Safety information

#### **CAUTION!**

Damages to property is likely if these warnings are not heeded.

Supplementary information and useful tips.

# 1.3 Safety information

# Applications conforming with specifications

The system is constructed and produced for:

- communication and process control

- general control and automation tasks

- industrial applications

- operation within the environmental conditions specified in the technical data

- installation into a cubicle

#### **DANGER!**

This device is not certified for applications in

in explosive environments (EX-zone)

#### **Documentation**

The manual must be available to all personnel in the

- project design department

- installation department

- commissioning

- operation

#### **CAUTION!**

The following conditions must be met before using or commissioning the components described in this manual:

- Hardware modifications to the process control system should only be carried out when the system has been disconnected from power!

- Installation and hardware modifications only by properly trained personnel.

- The national rules and regulations of the respective country must be satisfied (installation, safety, EMC ...)

#### **Disposal**

National rules and regulations apply to the disposal of the unit!

VIPA System SLIO Basics and mounting

Safety information for users

# 2 Basics and mounting

# 2.1 Safety information for users

Handling of electrostatic sensitive modules

VIPA modules make use of highly integrated components in MOS-Technology. These components are extremely sensitive to over-voltages that can occur during electrostatic discharges. The following symbol is attached to modules that can be destroyed by electrostatic discharges.

The Symbol is located on the module, the module rack or on packing material and it indicates the presence of electrostatic sensitive equipment. It is possible that electrostatic sensitive equipment is destroyed by energies and voltages that are far less than the human threshold of perception. These voltages can occur where persons do not discharge themselves before handling electrostatic sensitive modules and they can damage components thereby, causing the module to become inoperable or unusable. Modules that have been damaged by electrostatic discharges can fail after a temperature change, mechanical shock or changes in the electrical load. Only the consequent implementation of protection devices and meticulous attention to the applicable rules and regulations for handling the respective equipment can prevent failures of electrostatic sensitive modules.

#### Shipping of modules

Modules must be shipped in the original packing material.

Measurements and alterations on electrostatic sensitive modules When you are conducting measurements on electrostatic sensitive modules you should take the following precautions:

- Floating instruments must be discharged before use.

- Instruments must be grounded.

Modifying electrostatic sensitive modules you should only use soldering irons with grounded tips.

#### **CAUTION!**

Personnel and instruments should be grounded when working on electrostatic sensitive modules.

System conception > Overview

# 2.2 System conception

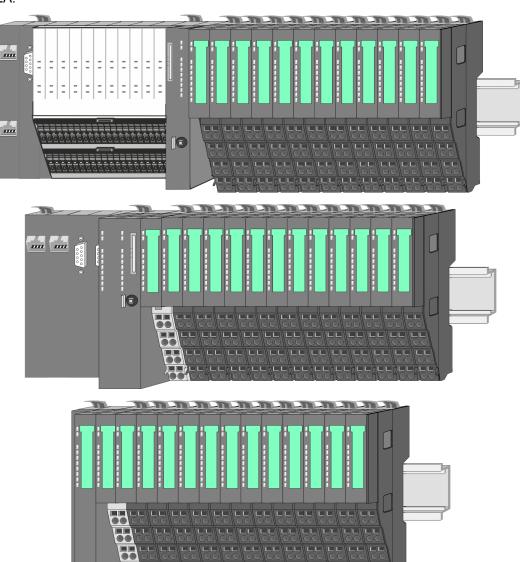

#### 2.2.1 Overview

System SLIO is a modular automation system for assembly on a 35mm mounting rail. By means of the peripheral modules with 2, 4 or 8 channels this system may properly be adapted matching to your automation tasks. The wiring complexity is low, because the supply of the DC 24V power section is integrated to the backplane bus and defective modules may be replaced with standing wiring. By deployment of the power modules in contrasting colors within the system, further isolated areas may be defined for the DC 24V power section supply, respectively the electronic power supply may be extended with 2A.

VIPA System SLIO Basics and mounting

System conception > Components

# 2.2.2 Components

- CPU (head module)

- Bus coupler (head module)

- Line extension

- Periphery modules

- Accessories

#### **CAUTION!**

Only modules of VIPA may be combined. A mixed operation with third-party modules is not allowed!

#### CPU 01xC

With this CPU 01xC, the CPU electronic, input/output components and power supply are integrated to one casing. In addition, up to 64 periphery modules of the System SLIO can be connected to the backplane bus. As head module via the integrated power supply CPU electronic and the I/O components are power supplied as well as the electronic of the connected periphery modules. To connect the power supply of the I/O components and for DC 24V power supply of via backplane bus connected peripheral modules, the CPU has removable connectors. By installing of up to 64 periphery modules at the backplane bus, these are electrically connected, this means these are assigned to the backplane bus, the electronic modules are power supplied and each periphery module is connected to the DC 24V power section supply.

#### CPU 01x

With this CPU 01x, the CPU electronic and power supply are integrated to one casing. As head module, via the integrated power module for power supply, CPU electronic and the electronic of the connected periphery modules are supplied. The DC 24 power section supply for the linked periphery modules is established via a further connection of the power module. By installing of up to 64 periphery modules at the backplane bus, these are electrically connected, this means these are assigned to the backplane bus, the electronic modules are power supplied and each periphery module is connected to the DC 24V power section supply.

### **CAUTION!**

CPU part and power module may not be separated! Here you may only exchange the electronic module!

## Bus coupler

With a bus coupler bus interface and power module is integrated to one casing. With the bus interface you get access to a subordinated bus system. As head module, via the integrated power module for power supply, bus interface and the electronic of the connected periphery modules are supplied. The DC 24 power section supply for the linked periphery modules is established via a further connection of the power module. By installing of up to 64 periphery modules at the bus coupler, these are electrically connected, this means these are assigned to the backplane bus, the electronic modules are power supplied and each periphery module is connected to the DC 24V power section supply.

#### CAUTION!

Bus interface and power module may not be separated! Here you may only exchange the electronic module!

System conception > Components

#### Line extension

In the System SLIO there is the possibility to place up to 64 modules in on line. By means of the line extension you can divide this line into several lines. Here you have to place a line extension master at each end of a line and the subsequent line has to start with a line extension slave. Master and slave are to be connected via a special connecting cable. In this way, you can divide a line on up to 5 lines. For each line extension the maximum number of pluggable modules at the System SLIO bus is decreased by 1. To use the line extension no special configuration is required.

Please note that some modules do not support line extensions due to the system. For more information, see the 'System SLIO - Compatibility List' at www.vipa.com

#### Periphery modules

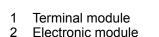

Each periphery module consists of a *terminal* and an *electronic module*.

- 1 Terminal module

- 2 Electronic module

#### Terminal module

The *terminal* module serves to carry the electronic module, contains the backplane bus with power supply for the electronic, the DC 24V power section supply and the staircase-shaped terminal for wiring. Additionally the terminal module has a locking system for fixing at a mounting rail. By means of this locking system your SLIO system may be assembled outside of your switchgear cabinet to be later mounted there as whole system.

#### Electronic module

The functionality of a SLIO periphery module is defined by the *electronic* module, which is mounted to the terminal module by a sliding mechanism. With an error the defective module may be exchanged for a functional module with standing installation. At the front side there are LEDs for status indication. For simple wiring each module shows a corresponding connection diagram at the front and at the side.

VIPA System SLIO Basics and mounting

System conception > Accessories

#### 2.2.3 Accessories

#### Shield bus carrier

The shield bus carrier (order no.: 000-0AB00) serves to carry the shield bus (10mm x 3mm) to connect cable shields. Shield bus carriers, shield bus and shield fixings are not in the scope of delivery. They are only available as accessories. The shield bus carrier is mounted underneath the terminal of the terminal module. With a flat mounting rail for adaptation to a flat mounting rail you may remove the spacer of the shield bus carrier.

#### **Bus cover**

With each head module, to protect the backplane bus connectors, there is a mounted bus cover in the scope of delivery. You have to remove the bus cover of the head module before mounting a System SLIO module. For the protection of the backplane bus connector you always have to mount the bus cover at the last module of your system again. The bus cover has the order no. 000-0AA00.

#### **Coding pins**

There is the possibility to fix the assignment of electronic and terminal module. Here coding pins (order number 000-0AC00) from VIPA can be used. The coding pin consists of a coding jack and a coding plug. By combining electronic and terminal module with coding pin, the coding jack remains in the electronic module and the coding plug in the terminal module. This ensures that after replacing the electronics module just another electronic module can be plugged with the same encoding.

**Dimensions**

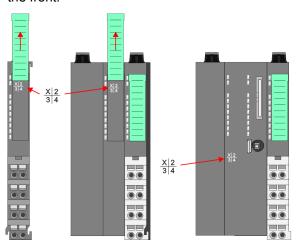

#### 2.2.4 Hardware revision

# Hardware revision on the front

- The hardware revision version is printed on every System SLIO module.

- Since a System SLIO module consists of a terminal and electronics module, you will find a hardware revision on each of them.

- Authoritative for the hardware revision of a System SLIO module is the hardware revision of the electronic module. This is always located under the labeling strip of the corresponding electronic module.

- On modules without labeling strip, such as CPUs, the hardware revision is printed on the front.

The example here shows the hardware revision 1. 1 is marked with X.

# Hardware revision via web server

On the CPUs and some bus couplers, you can output the hardware revision *'HW Revision'* via the integrated web server.

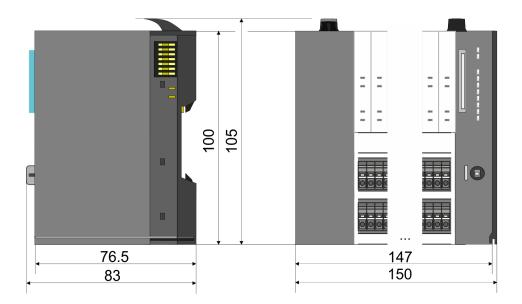

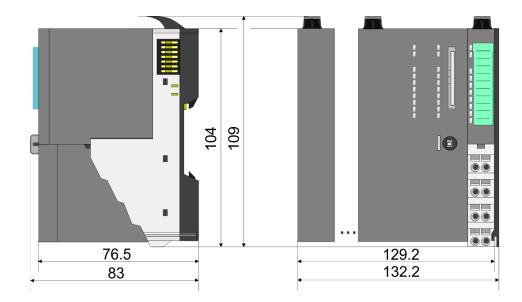

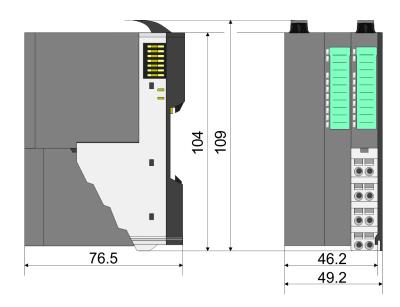

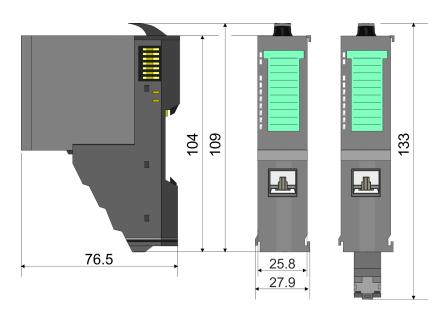

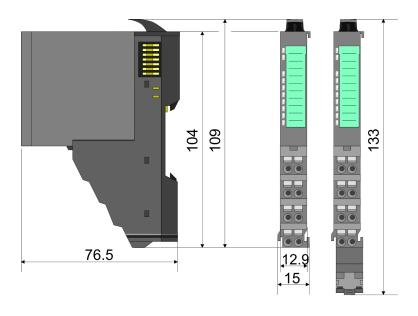

#### 2.3 Dimensions

## **Dimensions CPU 01xC**

VIPA System SLIO Basics and mounting

Dimensions

#### **Dimensions CPU 01x**

# Dimensions bus coupler and line extension slave

# Dimensions line extension master

Dimensions

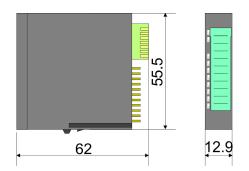

# Dimension periphery module

# Dimensions electronic module

Dimensions in mm

VIPA System SLIO

Basics and mounting

Mounting periphery modules

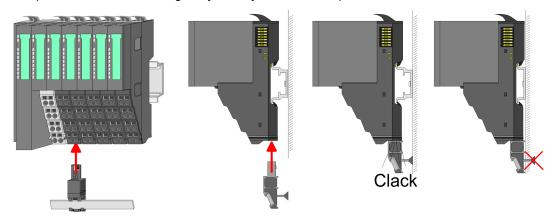

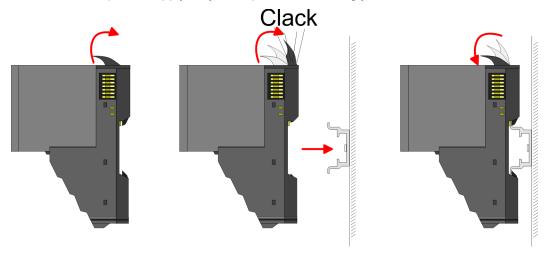

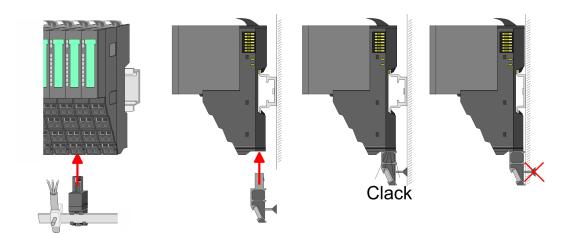

# 2.4 Mounting periphery modules

#### Requirements for UL compliance use

- Use for power supply exclusively SELV/PELV power supplies.

- The System SLIO must be installed and operated in a housing according to IEC 61010-1 9.3.2 c).

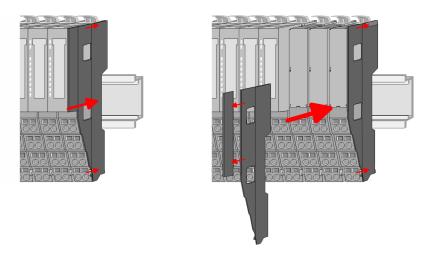

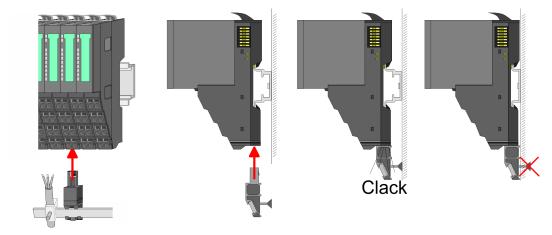

There is a locking lever at the top side of the module. For mounting and demounting this locking lever is to be turned upwards until this engages. For mounting place the module to the module installed before and push the module to the mounting rail guided by the strips at the upper and lower side of the module. The module is fixed to the mounting rail by pushing downward the locking lever. The modules may either separately be mounted to the mounting rail or as block. Here is to be considered that each locking lever is opened. The modules are each installed on a mounting rail. The electronic and power section supply are connected via the backplane bus. Up to 64 modules may be mounted. Please consider here that the sum current of the electronic power supply does not exceed the maximum value of 3A. By means of the power module 007-1AB10 the current of the electronic power supply may be expanded accordingly.

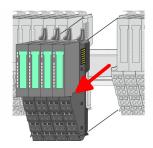

# Terminal and electronic module

For the exchange of a electronic module, the electronic module may be pulled forward after pressing the unlocking lever at the lower side of the module. For installation plug the electronic module guided by the strips at the lower side until this engages audible to the terminal module.

Each periphery module consists of a *terminal* and an *electronic module*.

Mounting periphery modules

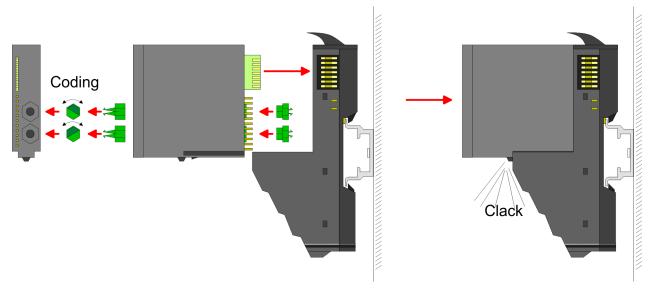

#### Coding

There is the possibility to fix the assignment of electronic and terminal module. Here coding pins (order number 000-0AC00) from VIPA can be used. The coding pin consists of a coding jack and a coding plug. By combining electronic and terminal module with coding pin, the coding jack remains in the electronic module and the coding plug in the terminal module. This ensures that after replacing the electronics module just another electronic module can be plugged with the same encoding.

Each electronic module has on its back 2 coding sockets for coding jacks. Due to the characteristics, with the coding jack 6 different positions can be plugged, each. Thus there are 36 possible combinations for coding with the use of both coding sockets.

- Plug, according to your coding, 2 coding jacks in the coding sockets of your electronic module until they lock

- **2.** Now plug the according coding plugs into the coding jacks.

- 3. To fix the coding put both the electronic and terminal module together until they lock

#### **CAUTION!**

Please consider that when replacing an already coded electronic module, this is always be replaced by an electronic module with the same coding.

Even with an existing coding on the terminal module, you can plug an electronic module without coding. The user is responsible for the correct usage of the coding pins. VIPA assumes no liability for incorrectly attached electronic modules or for damages which arise due to incorrect coding!

VIPA System SLIO **Basics and mounting**

Mounting periphery modules

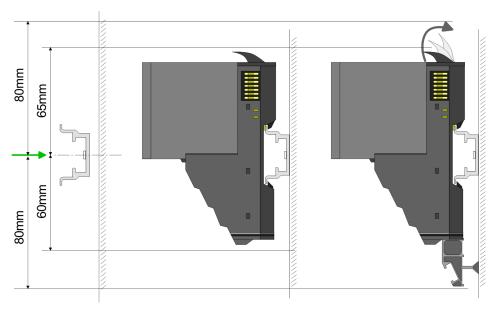

#### **Mounting periphery** modules

- 1. Mount the mounting rail! Please consider that a clearance from the middle of the mounting rail of at least 80mm above and 60mm below, respectively 80mm by deployment of shield bus carriers, exist.

- 2. Mount your head module such as CPU or field bus coupler.

- 3. Before mounting the periphery modules you have to remove the bus cover at the right side of the Head module by pulling it forward. Keep the cover for later mounting.

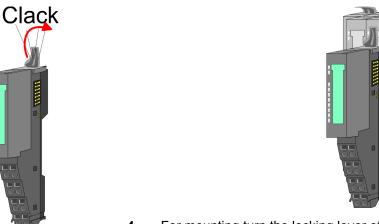

- **4.** For mounting turn the locking lever of the module upward until it engages.

- For mounting place the module to the module installed before and push the module to the mounting rail guided by the strips at the upper and lower side of the module.

- **6.** Turn the locking lever of the periphery module downward, again.

Wiring periphery modules

After mounting the whole system, to protect the backplane bus connectors at the last module you have to mount the bus cover, now. If the last module is a clamp module, for adaptation the upper part of the bus cover is to be removed.

# 2.5 Wiring periphery modules

#### **Terminal module terminals**

#### **CAUTION!**

## Do not connect hazardous voltages!

If this is not explicitly stated in the corresponding module description, hazardous voltages are not allowed to be connected to the corresponding terminal module!

With wiring the terminal modules, terminals with spring clamp technology are used for wiring. The spring clamp technology allows quick and easy connection of your signal and supply lines. In contrast to screw terminal connections this type of connection is vibration proof.

#### Data

U<sub>max</sub> 240V AC / 30V DC

$I_{\text{max}}$  10A

Cross section 0.08 ... 1.5mm<sup>2</sup> (AWG 28 ... 16)

Stripping length 10mm

VIPA System SLIO Basics and mounting

Wiring periphery modules

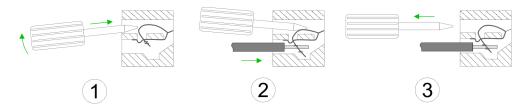

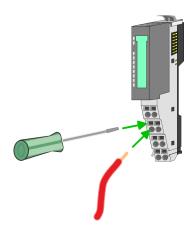

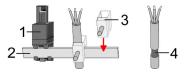

#### Wiring procedure

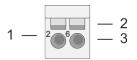

- 1 Pin number at the connector

- 2 Opening for screwdriver

- 3 Connection hole for wire

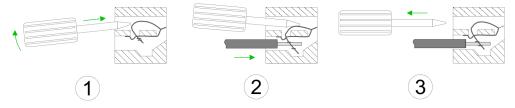

- 1. Insert a suited screwdriver at an angel into the square opening as shown. Press and hold the screwdriver in the opposite direction to open the contact spring.

- 2. Insert the stripped end of wire into the round opening. You can use wires with a cross section of 0.08mm<sup>2</sup> up to 1.5mm<sup>2</sup>

- **3.** By removing the screwdriver, the wire is securely fixed via the spring contact to the terminal.

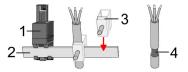

**Shield attachment**

- 1 Shield bus carrier

- 2 Shield bus (10mm x 3mm)

- 3 Shield clamp

- 4 Cable shield

To attach the shield the mounting of shield bus carriers are necessary. The shield bus carrier (available as accessory) serves to carry the shield bus to connect cable shields.

- **1.** Each System SLIO module has a carrier hole for the shield bus carrier. Push the shield bus carrier, until they engage into the module. With a flat mounting rail for adaptation to a flat mounting rail you may remove the spacer of the shield bus carrier.

- 2. Put your shield bus into the shield bus carrier.

**3.** Attach the cables with the accordingly stripped cable screen and fix it by the shield clamp with the shield bus.

VIPA System SLIO **Basics and mounting**

Wiring power modules

# 2.6 Wiring power modules

#### **Terminal module terminals**

Power modules are either integrated to the head module or may be installed between the periphery modules. With power modules, terminals with spring clamp technology are used for wiring. The spring clamp technology allows quick and easy connection of your signal and supply lines. In contrast to screw terminal connections this type of connection is vibration proof.

#### **Data**

$U_{\text{max}}$ 30V DC 10A  $I_{max}$

0.08 ... 1.5mm<sup>2</sup> (AWG 28 ... 16) Cross section

Stripping length 10mm

## Wiring procedure

Pin number at the connector

Opening for screwdriver

2 Connection hole for wire

- Insert a suited screwdriver at an angel into the square opening as shown. Press and hold the screwdriver in the opposite direction to open the contact spring.

- 2. Insert the stripped end of wire into the round opening. You can use wires with a cross section of 0.08mm<sup>2</sup> up to 1.5mm<sup>2</sup>

- By removing the screwdriver, the wire is securely fixed via the spring contact to the terminal.

VIPA System SLIO

Basics and mounting

Wiring power modules

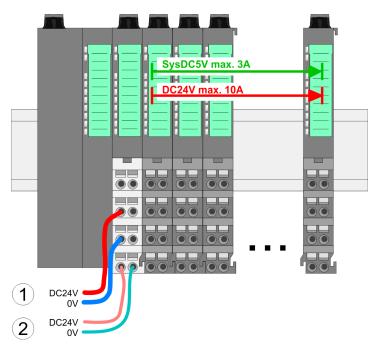

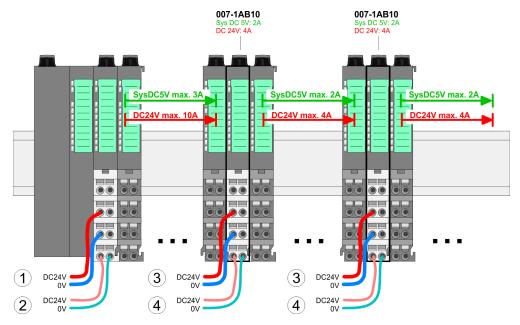

#### Standard wiring

- (1) DC 24V for power section supply I/O area (max. 10A)

- (2) DC 24V for electronic power supply bus coupler and I/O area

PM - Power module

For wires with a core cross-section of 0.08mm<sup>2</sup> up to 1.5mm<sup>2</sup>.

| Pos. | Function   | Туре | Description                          |

|------|------------|------|--------------------------------------|

| 1    |            |      | not connected                        |

| 2    | DC 24V     | I    | DC 24V for power section supply      |

| 3    | 0V         | I    | GND for power section supply         |

| 4    | Sys DC 24V | I    | DC 24V for electronic section supply |

| 5    |            |      | not connected                        |

| 6    | DC 24V     | I    | DC 24V for power section supply      |

| 7    | 0V         | I    | GND for power section supply         |

| 8    | Sys 0V     | I    | GND for electronic section supply    |

I: Input

#### **CAUTION!**

Since the power section supply is not internally protected, it is to be externally protected with a fuse, which corresponds to the maximum current. This means max. 10A is to be protected by a 10A fuse (fast) respectively by a line circuit breaker 10A characteristics Z!

The electronic power section supply is internally protected against higher voltage by fuse. The fuse is within the power module. If the fuse releases, its electronic module must be exchanged!

Wiring power modules

#### **Fusing**

■ The power section supply is to be externally protected with a fuse, which corresponds to the maximum current. This means max. 10A is to be protected with a 10A fuse (fast) respectively by a line circuit breaker 10A characteristics Z!

- It is recommended to externally protect the electronic power supply for head modules and I/O area with a 2A fuse (fast) respectively by a line circuit breaker 2A characteristics Z.

- The electronic power supply for the I/O area of the power module 007-1AB10 should also be externally protected with a 1A fuse (fast) respectively by a line circuit breaker 1A characteristics Z.

# State of the electronic power supply via LEDs

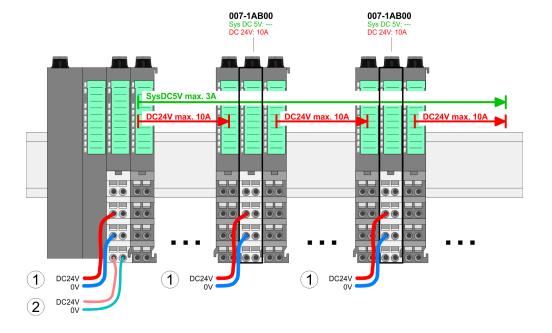

After PowerON of the System SLIO the LEDs RUN respectively MF get on so far as the sum current does not exceed 3A. With a sum current greater than 3A the LEDs may not be activated. Here the power module with the order number 007-1AB10 is to be placed between the peripheral modules.

# Deployment of the power modules

- If the 10A for the power section supply is no longer sufficient, you may use the power module from VIPA with the order number 007-1AB00. So you have also the possibility to define isolated groups.

- The power module with the order number 007-1AB10 is to be used if the 3A for the electronic power supply at the backplane bus is no longer sufficient. Additionally you get an isolated group for the DC 24V power section supply with max. 4A.

- By placing the power module 007-1AB10 at the following backplane bus modules may be placed with a sum current of max. 2A. Afterwards a power module is to be placed again. To secure the power supply, the power modules may be mixed used.

#### Power module 007-1AB00

VIPA System SLIO **Basics and mounting**

Wiring power modules

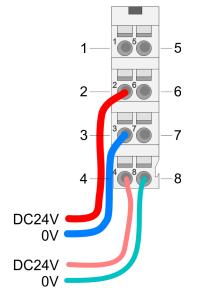

#### Power module 007-1AB10

- (1) DC 24V for power section supply I/O area (max. 10A)

- (2) DC 24V for electronic power supply bus coupler and I/O area (3) DC 24V for power section supply I/O area (max. 4A)

- (4) DC 24V for electronic power supply I/O area

#### Shield attachment

- Shield bus carrier

- 2 Shield bus (10mm x 3mm)

- Shield clamp 3

- Cable shield

To attach the shield the mounting of shield bus carriers are necessary. The shield bus carrier (available as accessory) serves to carry the shield bus to connect cable shields.

- 1. Each System SLIO module has a carrier hole for the shield bus carrier. Push the shield bus carrier, until they engage into the module. With a flat mounting rail for adaptation to a flat mounting rail you may remove the spacer of the shield bus carrier.

- 2. Put your shield bus into the shield bus carrier.

Demounting periphery modules

**3.** Attach the cables with the accordingly stripped cable screen and fix it by the shield clamp with the shield bus.

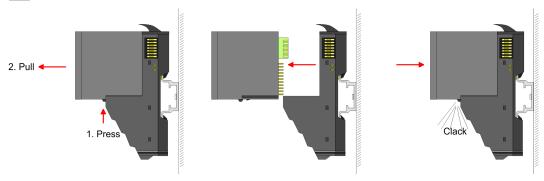

# 2.7 Demounting periphery modules

#### **Proceeding**

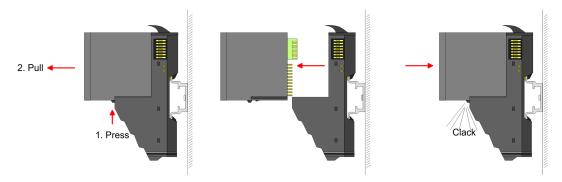

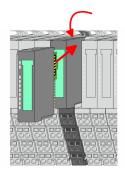

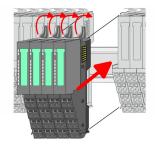

# Exchange of an electronic module

1. Power-off your system.

- **2.** For the exchange of a electronic module, the electronic module may be pulled forward after pressing the unlocking lever at the lower side of the module.

- **3.** For installation plug the new electronic module guided by the strips at the lower side until this engages to the terminal module.

- ⇒ Now you can bring your system back into operation.

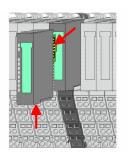

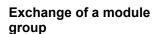

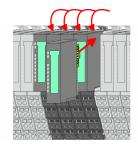

# Exchange of a periphery module

- **1.** Power-off your system.

- **2.** Remove if exists the wiring of the module.

- 3.

For demounting and exchange of a (head) module or a group of modules, due to mounting reasons you always have to remove the electronic module <u>right</u> beside. After mounting it may be plugged again.

Press the unlocking lever at the lower side of the just mounted right module and pull it forward.

VIPA System SLIO

Basics and mounting

Demounting periphery modules

**4.** Turn the locking lever of the module to be exchanged upwards.

- **5.** Pull the module.

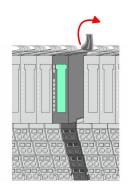

- **6.** For mounting turn the locking lever of the module to be mounted upwards.

- 7. To mount the module put it to the gap between the both modules and push it, guided by the stripes at both sides, to the mounting rail.

- **8.** Turn the locking lever downward, again.

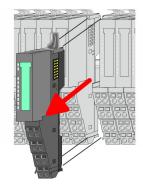

- **9.** Plug again the electronic module, which you have removed before.

- **10.** Wire your module.

- ⇒ Now you can bring your system back into operation.

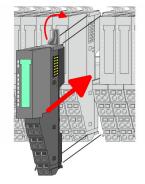

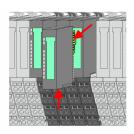

- **1.** Power-off your system.

- **2.** Remove if exists the wiring of the module group.

3.

For demounting and exchange of a (head) module or a group of modules, due to mounting reasons you always have to remove the electronic module <u>right</u> beside. After mounting it may be plugged again.

Press the unlocking lever at the lower side of the just mounted right module near the module group and pull it forward.

Demounting periphery modules > Easy Maintenance

**4.** Turn all the locking lever of the module group to be exchanged upwards.

- **5.** Pull the module group forward.

- **6.** For mounting turn all the locking lever of the module group to be mounted upwards.

- 7. To mount the module group put it to the gap between the both modules and push it, guided by the stripes at both sides, to the mounting rail.

- **8.** Turn all the locking lever downward, again.

- **9.** Plug again the electronic module, which you have removed before.

- **10.** Wire your module group.

- ⇒ Now you can bring your system back into operation.

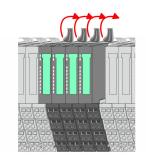

## 2.7.1 Easy Maintenance

### **Easy Maintenance**

Easy Maintenance means the support for adding and removing modules during operation without having to restart the system. For details, refer to the manual for your head module.

VIPA System SLIO

Basics and mounting

Trouble shooting - LEDs

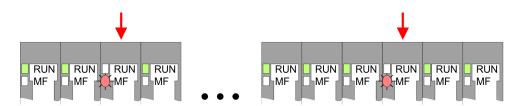

## 2.8 Trouble shooting - LEDs

#### General

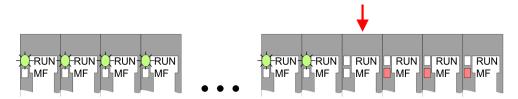

Each module has the LEDs RUN and MF on its front side. Errors or incorrect modules may be located by means of these LEDs.

In the following illustrations flashing LEDs are marked by \tilde{\pi}.

Sum current of the electronic power supply exceeded

Behaviour: After PowerON the RUN LED of each module is off and the MF LED of each module is sporadically on.

*Reason*: The maximum current for the electronic power supply is exceeded.

Remedy: As soon as the sum current of the electronic power supply is exceeded, always place the power module 007-1AB10. & Chap. 2.6 'Wiring power modules' page 20

#### Error in configuration

*Behaviour*: After PowerON the MF LED of one module respectively more modules flashes. The RUN LED remains off.

Reason: At this position a module is placed, which does not correspond to the configured module.

Remedy: Match configuration and hardware structure.

#### Module failure

*Behaviour*: After PowerON all of the RUN LEDs up to the defective module are flashing. With all following modules the MF LED is on and the RUN LED is off.

*Reason*: The module on the right of the flashing modules is defective.

Remedy: Replace the defective module.

Installation guidelines

## 2.9 Installation guidelines

#### General

The installation guidelines contain information about the interference free deployment of a PLC system. There is the description of the ways, interference may occur in your PLC, how you can make sure the electromagnetic compatibility (EMC), and how you manage the isolation.

#### What does EMC mean?

Electromagnetic compatibility (EMC) means the ability of an electrical device, to function error free in an electromagnetic environment without being interfered respectively without interfering the environment.

The components of VIPA are developed for the deployment in industrial environments and meets high demands on the EMC. Nevertheless you should project an EMC planning before installing the components and take conceivable interference causes into account.

# Possible interference causes

Electromagnetic interferences may interfere your control via different ways:

- Electromagnetic fields (RF coupling)

- Magnetic fields with power frequency

- Bus system

- Power supply

- Protected earth conductor

Depending on the spreading medium (lead bound or lead free) and the distance to the interference cause, interferences to your control occur by means of different coupling mechanisms.

#### There are:

- galvanic coupling

- capacitive coupling

- inductive coupling

- radiant coupling

#### Basic rules for EMC

In the most times it is enough to take care of some elementary rules to guarantee the EMC. Please regard the following basic rules when installing your PLC.

- Take care of a correct area-wide grounding of the inactive metal parts when installing your components.

- Install a central connection between the ground and the protected earth conductor system.

- Connect all inactive metal extensive and impedance-low.

- Please try not to use aluminium parts. Aluminium is easily oxidizing and is therefore less suitable for grounding.

- When cabling, take care of the correct line routing.

- Organize your cabling in line groups (high voltage, current supply, signal and data lines).

- Always lay your high voltage lines and signal respectively data lines in separate channels or bundles.

- Route the signal and data lines as near as possible beside ground areas (e.g. suspension bars, metal rails, tin cabinet).

VIPA System SLIO Basics and mounting

Installation guidelines

- Proof the correct fixing of the lead isolation.

- Data lines must be laid isolated.

- Analog lines must be laid isolated. When transmitting signals with small amplitudes the one sided laying of the isolation may be favourable.

- Lay the line isolation extensively on an isolation/protected earth conductor rail directly after the cabinet entry and fix the isolation with cable clamps.

- Make sure that the isolation/protected earth conductor rail is connected impedance-low with the cabinet.

- Use metallic or metallised plug cases for isolated data lines.

- In special use cases you should appoint special EMC actions.

- Consider to wire all inductivities with erase links.

- Please consider luminescent lamps can influence signal lines.

- Create a homogeneous reference potential and ground all electrical operating supplies when possible.

- Please take care for the targeted employment of the grounding actions. The grounding of the PLC serves for protection and functionality activity.

- Connect installation parts and cabinets with your PLC in star topology with the isolation/protected earth conductor system. So you avoid ground loops.

- If there are potential differences between installation parts and cabinets, lay sufficiently dimensioned potential compensation lines.

#### Isolation of conductors

Electrical, magnetically and electromagnetic interference fields are weakened by means of an isolation, one talks of absorption. Via the isolation rail, that is connected conductive with the rack, interference currents are shunt via cable isolation to the ground. Here you have to make sure, that the connection to the protected earth conductor is impedancelow, because otherwise the interference currents may appear as interference cause.

When isolating cables you have to regard the following:

- If possible, use only cables with isolation tangle.

- The hiding power of the isolation should be higher than 80%.

- Normally you should always lay the isolation of cables on both sides. Only by means of the both-sided connection of the isolation you achieve high quality interference suppression in the higher frequency area. Only as exception you may also lay the isolation one-sided. Then you only achieve the absorption of the lower frequencies. A one-sided isolation connection may be convenient, if:

- the conduction of a potential compensating line is not possible.

- analog signals (some mV respectively μA) are transferred.

- foil isolations (static isolations) are used.

- With data lines always use metallic or metallised plugs for serial couplings. Fix the isolation of the data line at the plug rack. Do not lay the isolation on the PIN 1 of the plug bar!

- At stationary operation it is convenient to strip the insulated cable interruption free and lay it on the isolation/protected earth conductor line.

- To fix the isolation tangles use cable clamps out of metal. The clamps must clasp the isolation extensively and have well contact.

- Lay the isolation on an isolation rail directly after the entry of the cable in the cabinet. Lead the isolation further on to your PLC and don't lay it on there again!

#### **CAUTION!**

## Please regard at installation!

At potential differences between the grounding points, there may be a compensation current via the isolation connected at both sides.

Remedy: Potential compensation line

General data

# 2.10 General data

| Conformity and approval |            |                                                                                               |

|-------------------------|------------|-----------------------------------------------------------------------------------------------|

| Conformity              |            |                                                                                               |

| CE                      | 2014/35/EU | Low-voltage directive                                                                         |

|                         | 2014/30/EU | EMC directive                                                                                 |

| Approval                |            |                                                                                               |

| UL                      | -          | Refer to Technical data                                                                       |

| others                  |            |                                                                                               |

| RoHS                    | 2011/65/EU | Restriction of the use of certain hazardous substances in electrical and electronic equipment |

| Protection of persons and device protection |   |                                   |  |  |

|---------------------------------------------|---|-----------------------------------|--|--|

| Type of protection                          | - | IP20                              |  |  |

| Electrical isolation                        |   |                                   |  |  |

| to the field bus                            | - | electrically isolated             |  |  |

| to the process level                        | - | electrically isolated             |  |  |

| Insulation resistance                       | - | -                                 |  |  |

| Insulation voltage to reference earth       |   |                                   |  |  |

| Inputs / outputs                            | - | AC / DC 50V, test voltage AC 500V |  |  |

| Protective measures                         | - | against short circuit             |  |  |

| Environmental conditions to EN 61131-2 |               |                                                 |  |  |  |

|----------------------------------------|---------------|-------------------------------------------------|--|--|--|

| Climatic                               |               |                                                 |  |  |  |

| Storage / transport                    | EN 60068-2-14 | -25+70°C                                        |  |  |  |

| Operation                              |               |                                                 |  |  |  |

| Horizontal installation hanging        | EN 61131-2    | 0+60°C                                          |  |  |  |

| Horizontal installation lying          | EN 61131-2    | 0+55°C                                          |  |  |  |

| Vertical installation                  | EN 61131-2    | 0+50°C                                          |  |  |  |

| Air humidity                           | EN 60068-2-30 | RH1 (without condensation, rel. humidity 1095%) |  |  |  |

| Pollution                              | EN 61131-2    | Degree of pollution 2                           |  |  |  |

| Installation altitude max.             | -             | 2000m                                           |  |  |  |

| Mechanical                             |               |                                                 |  |  |  |

| Oscillation                            | EN 60068-2-6  | 1g, 9Hz 150Hz                                   |  |  |  |

| Shock                                  | EN 60068-2-27 | 15g, 11ms                                       |  |  |  |

VIPA System SLIO Basics and mounting

General data

| Mounting conditions |   |                         |  |

|---------------------|---|-------------------------|--|

| Mounting place      | - | In the control cabinet  |  |

| Mounting position   | - | Horizontal and vertical |  |

| EMC                  | Standard     |              | Comment                                         |

|----------------------|--------------|--------------|-------------------------------------------------|

| Emitted interference | EN 61000-6-4 |              | Class A (Industrial area)                       |

| Noise immunity       | EN 61000-6-2 |              | Industrial area                                 |

| zone B               |              | EN 61000-4-2 | ESD                                             |

|                      |              |              | 8kV at air discharge (degree of severity 3),    |

|                      |              |              | 4kV at contact discharge (degree of severity 2) |

|                      |              | EN 61000-4-3 | HF field immunity (casing)                      |

|                      |              |              | 80MHz 1000MHz, 10V/m, 80% AM (1kHz)             |

|                      |              |              | 1.4GHz 2.0GHz, 3V/m, 80% AM (1kHz)              |

|                      |              |              | 2GHz 2.7GHz, 1V/m, 80% AM (1kHz)                |

|                      |              | EN 61000-4-6 | HF conducted                                    |

|                      |              |              | 150kHz 80MHz, 10V, 80% AM (1kHz)                |

|                      |              | EN 61000-4-4 | Burst, degree of severity 3                     |

|                      |              | EN 61000-4-5 | Surge, degree of severity 3 *                   |

<sup>\*)</sup> Due to the high-energetic single pulses with Surge an appropriate external protective circuit with lightning protection elements like conductors for lightning and overvoltage is necessary.

Hardware description VIPA System SLIO

Structure

# 3 Hardware description

# 3.1 Properties

#### **Features**

- 1 counter 32bit (AB) invertible, DC 24V

- Counting frequency max 400kHz (AB 1/2/4-fold evaluation or pulse and direction)

- Latch value, comparison value, set value, input filter (configurable)

- HW gate, reset, digital output for comparison

- Interrupt and diagnostics function with µs time stamp

- µs time stamp for counter value (e.g. for speed calculation)

#### Order data

| Туре   | Order number | Description                     |

|--------|--------------|---------------------------------|

| FM 050 | 050-1BA00    | Counter module advanced 1x32bit |

|        |              | DC 24V, DO 1xDC 24V 0.5A        |

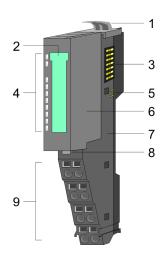

# 3.2 Structure

#### 050-1BA00

- 1 Locking lever terminal module

- 2 Labeling strip

- 3 Backplane bus

- 4 LED status indication

- DC 24V power section supply

- B Electronic module

- 7 Terminal module

- B Locking lever electronic module

- 9 Terminal

Structure

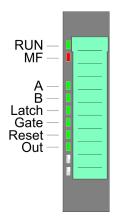

## **Status indication**

| LED      |                                                     | Description                                                          |  |  |  |  |

|----------|-----------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| RUN      | MF                                                  |                                                                      |  |  |  |  |

| green    | red                                                 |                                                                      |  |  |  |  |

|          |                                                     |                                                                      |  |  |  |  |

| •        | 0                                                   | Bus communication is OK  Module status is OK                         |  |  |  |  |

|          | •                                                   | Bus communication is OK                                              |  |  |  |  |

| <u> </u> |                                                     | Module status reports an error                                       |  |  |  |  |

| 0        |                                                     | Bus communication is not possible                                    |  |  |  |  |

|          | _                                                   | Module status reports an error                                       |  |  |  |  |

| 0        | 0                                                   | Error at bus power supply                                            |  |  |  |  |

| Х        | В                                                   | Error in configuration ♥ Chap. 2.8 'Trouble shooting - LEDs' page 27 |  |  |  |  |

|          |                                                     |                                                                      |  |  |  |  |

| Α        | green                                               | Digital input 1                                                      |  |  |  |  |

| , ,      |                                                     | A/pulse is set                                                       |  |  |  |  |

| В        | green                                               | Digital input 5                                                      |  |  |  |  |

|          |                                                     | B/direction is set                                                   |  |  |  |  |

| Latch    | green                                               | Digital input 4                                                      |  |  |  |  |

|          |                                                     | Latch is set                                                         |  |  |  |  |

| Gate     | green                                               | Digital input 8                                                      |  |  |  |  |

|          |                                                     | hardware gate is set                                                 |  |  |  |  |

| Reset    | green                                               | Digital input 7                                                      |  |  |  |  |

|          |                                                     | Reset is set                                                         |  |  |  |  |

| OUT      | green                                               | Digital output 6 is set                                              |  |  |  |  |

|          | on; a Loff; a Liblinka with 2Hz; B Lost relevant; V |                                                                      |  |  |  |  |

on: • | off: ○ | blinks with 2Hz: B | not relevant: X

Hardware description VIPA System SLIO

Structure

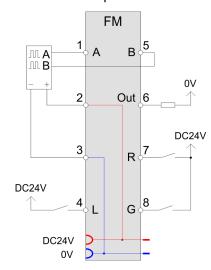

# Pin assignment

For wires with a cross section of 0.08mm<sup>2</sup> up to 1.5mm<sup>2</sup>.

| Pos. | Function | Туре | Description                                                                                                                                                          |

|------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Α        | I    | A / pulse                                                                                                                                                            |

|      |          |      | Pulse input for counter signal respectively track A of an encoder for 1-, 2- or 4-fold evaluation.                                                                   |

| 2    | DC 24V   | 0    | DC 24V for encoder                                                                                                                                                   |

| 3    | 0V       | 0    | GND                                                                                                                                                                  |

| 4    | L        | I    | Latch                                                                                                                                                                |

|      |          |      | Input to store the current <i>counter value</i> as <i>latch value</i> in the input area. The storage happens with an edge 0-1 respectively a level-triggered signal. |

| 5    | В        | I    | B / direction                                                                                                                                                        |

|      |          |      | direction signal respectively track B of an encoder (invertible via parameterization)                                                                                |

| 6    | Out      | 0    | Digital output controlled by means of the comparison functions.                                                                                                      |

| 7    | R        | I    | Reset                                                                                                                                                                |

|      |          |      | Input to reset the counter, if the reset functionality was enabled within the parameterization.                                                                      |

| 8    | G        | I    | Hardware gate                                                                                                                                                        |

|      |          |      | Input to control the HW gate. The HW gate is controlled by a high level.                                                                                             |

I: Input, O: Output

VIPA System SLIO Hardware description

Technical data

# 3.3 Technical data

| Order no.                                                           | 050-1BA00           |

|---------------------------------------------------------------------|---------------------|

| Туре                                                                | FM 050              |

| Module ID                                                           | 08C1 3800           |

| Current consumption/power loss                                      |                     |

| Current consumption from backplane bus                              | 75 mA               |

| Power loss                                                          | 1 W                 |

| Technical data digital inputs                                       |                     |

| Number of inputs                                                    | 5                   |

| Cable length, shielded                                              | 100 m               |

| Cable length, unshielded                                            | -                   |

| Rated load voltage                                                  | DC 20.428.8 V       |

| Reverse polarity protection of rated load voltage                   | -                   |

| Current consumption from load voltage L+ (without load)             | 20 mA               |

| Rated value                                                         | DC 20.428.8 V       |

| Input voltage for signal "0"                                        | DC 05 V             |

| Input voltage for signal "1"                                        | DC 1528.8 V         |

| Input voltage hysteresis                                            | -                   |

| Signal logic input                                                  | Sinking input       |

| Frequency range                                                     | -                   |

| Input resistance                                                    | -                   |

| Input current for signal "1"                                        | 3 mA                |

| Connection of Two-Wire-BEROs possible                               | ✓                   |

| Max. permissible BERO quiescent current                             | 0.5 mA              |

| Input delay of "0" to "1"                                           | 0.8 μs              |

| Input delay of "1" to "0"                                           | 0.8 μs              |

| Number of simultaneously utilizable inputs horizontal configuration | 5                   |

| Number of simultaneously utilizable inputs vertical configuration   | 5                   |

| Input characteristic curve                                          | IEC 61131-2, type 1 |

| Initial data size                                                   | 12 Byte             |

| Technical data digital outputs                                      |                     |

| Number of outputs                                                   | 1                   |

| Cable length, shielded                                              | 100 m               |

| Cable length, unshielded                                            | 100 m               |

| Rated load voltage                                                  | DC 20.428.8 V       |

| Current consumption from load voltage L+ (without load)             | -                   |

Hardware description VIPA System SLIO

Technical data

| Order no.                                                     | 050-1BA00            |

|---------------------------------------------------------------|----------------------|

| Output delay of "0" to "1"                                    | 30 µs                |

| Output delay of "1" to "0"                                    | 30 μs                |

| Minimum load current                                          | -                    |

| Lamp load                                                     | 10 W                 |

| Parallel switching of outputs for redundant control of a load | not possible         |

| Parallel switching of outputs for increased power             | not possible         |

| Actuation of digital input                                    | ✓                    |

| Switching frequency with resistive load                       | max. 10 kHz          |

| Switching frequency with inductive load                       | max. 0.5 Hz          |

| Switching frequency on lamp load                              | max. 10 kHz          |

| Internal limitation of inductive shut-off voltage             | L+ (-52 V)           |

| Short-circuit protection of output                            | yes, electronic      |

| Trigger level                                                 | 1 A                  |

| Number of operating cycle of relay outputs                    | -                    |

| Switching capacity of contacts                                | -                    |

| Output data size                                              | 10 Byte              |

| Technical data counters                                       |                      |

| Number of counters                                            | 1                    |

| Counter width                                                 | 32 Bit               |

| Maximum input frequency                                       | 100 kHz              |

| Maximum count frequency                                       | 400 kHz              |

| Mode incremental encoder                                      | ✓                    |

| Mode pulse / direction                                        | ✓                    |

| Mode pulse                                                    | -                    |

| Mode frequency counter                                        | -                    |

| Mode period measurement                                       | -                    |

| Gate input available                                          | ✓                    |

| Latch input available                                         | ✓                    |

| Reset input available                                         | ✓                    |

| Counter output available                                      | ✓                    |

| Status information, alarms, diagnostics                       |                      |

| Status display                                                | yes                  |

| Interrupts                                                    | yes, parameterizable |

| Process alarm                                                 | yes, parameterizable |

| Diagnostic interrupt                                          | yes, parameterizable |

| Diagnostic functions                                          | yes, parameterizable |

VIPA System SLIO Hardware description

Technical data

| Order no.                                                   | 050-1BA00                  |

|-------------------------------------------------------------|----------------------------|

| Diagnostics information read-out                            | possible                   |

| Module state                                                | green LED                  |

| Module error display                                        | red LED                    |

| Channel error display                                       | none                       |

| Isolation                                                   |                            |

| Between channels                                            | -                          |

| Between channels of groups to                               | -                          |

| Between channels and backplane bus                          | ✓                          |

| Between channels and power supply                           | -                          |

| Max. potential difference between circuits                  | -                          |

| Max. potential difference between inputs (Ucm)              | -                          |

| Max. potential difference between Mana and Mintern (Uiso)   | -                          |

| Max. potential difference between inputs and Mana (Ucm)     | -                          |

| Max. potential difference between inputs and Mintern (Uiso) | -                          |

| Max. potential difference between Mintern and outputs       | -                          |

| Insulation tested with                                      | DC 500 V                   |

| Datasizes                                                   |                            |

| Input bytes                                                 | 12                         |

| Output bytes                                                | 10                         |

| Parameter bytes                                             | 25                         |

| Diagnostic bytes                                            | 20                         |

| Housing                                                     |                            |

| Material                                                    | PPE / PPE GF10             |

| Mounting                                                    | Profile rail 35 mm         |

| Mechanical data                                             |                            |

| Dimensions (WxHxD)                                          | 12.9 mm x 109 mm x 76.5 mm |

| Net weight                                                  | 57 g                       |

| Weight including accessories                                | 57 g                       |

| Gross weight                                                | 71 g                       |

| Environmental conditions                                    |                            |

| Operating temperature                                       | 0 °C to 60 °C              |

| Storage temperature                                         | -25 °C to 70 °C            |

| Certifications                                              |                            |

| UL certification                                            | yes                        |

| KC certification                                            | yes                        |

Fast introduction

# 4 Deployment

# 4.1 Fast introduction

#### Counter range

| Limits              | Valid range of values               |

|---------------------|-------------------------------------|

| Lower counter limit | -2 147 483 648 (-2 <sup>31</sup> )  |

| Upper counter limit | +2 147 483 647 (2 <sup>31</sup> -1) |

The maximum counter frequency is 400kHz.

#### Address areas

#### Input area

At CPU, PROFIBUS and PROFINET the input area is embedded to the corresponding address area.

IX - Index for access via CANopen

SX - Subindex for access via EtherCAT with Index 6000h + EtherCAT-Slot

More can be found in the according manual of your bus coupler.

| Addr. | Name   | Bytes | Function       | IX    | SX  |

|-------|--------|-------|----------------|-------|-----|

| +0    | CV_I   | 4     | Counter value  | 5400h | 01h |

| +4    | CL_I   | 4     | Latch value    | 5401h | 02h |

| +8    | CSTS_I | 2     | Counter status | 5402h | 03h |

| +10   | C_US   | 2     | μs ticker      | 5403h | 04h |

#### Output area

At CPU, PROFIBUS and PROFINET the output area is embedded to the corresponding address area.

IX - Index for access via CANopen

SX - Subindex for access via EtherCAT with Index 7000h + EtherCAT-Slot

More can be found in the according manual of your bus coupler.

| Addr. | Name    | Bytes | Function         | IX    | SX  |

|-------|---------|-------|------------------|-------|-----|

| +0    | CC_I    | 4     | Comparison value | 5600h | 01h |

| +4    | CS_I    | 4     | Set value        | 5601h | 02h |

| +8    | CCTRL_I | 2     | Control word     | 5602h | 03h |

# CSTS\_I Counter status

| Bit | Name        | Function                                                 |

|-----|-------------|----------------------------------------------------------|

| 0   | STS_SYNC    | Reset was active                                         |

| 1   | STS_CTRL_DO | Is set when digital output is enabled                    |

| 2   | STS_SW-GATE | Status software gate (set when <i>SW</i> gate is active) |

| 3   | STS_RST     | Status reset input                                       |

Fast introduction

| Bit                                                                  | Name      | Function                                                            |  |  |

|----------------------------------------------------------------------|-----------|---------------------------------------------------------------------|--|--|

| 4                                                                    | STS_STRT  | Status hardware gate                                                |  |  |

|                                                                      |           | (set when HW gate is active)                                        |  |  |

| 5                                                                    | STS_GATE  | Status internal gate                                                |  |  |

|                                                                      |           | (set when internal gate active)                                     |  |  |

| 6                                                                    | STS_DO    | Status digital counter output (DO)                                  |  |  |

| 7                                                                    | STS_C_DN  | Status set at counter direction backward                            |  |  |

| 8                                                                    | STS_C_UP  | Status set at counter direction forward                             |  |  |

| 9                                                                    | STS_CMP*  | Status comparison is set when the comparison condition is met.      |  |  |

|                                                                      |           | If comparison is parameterized <i>never</i> , the bit is never set. |  |  |

| 10                                                                   | STS_END*  | Status is set                                                       |  |  |

|                                                                      |           | when end value was reached                                          |  |  |

| 11                                                                   | STS_OFLW* | Status is set at overflow                                           |  |  |

| 12                                                                   | STS_UFLW* | Status is set at underflow                                          |  |  |

| 13                                                                   | STS_ZP*   | Status is set at zero run                                           |  |  |

| 14                                                                   | STS_LTCH  | Status of the latch input                                           |  |  |

| 15                                                                   | -         | reserved                                                            |  |  |

| *) The hite remain set until reset with DES_SET (hit 6 control word) |           |                                                                     |  |  |

$<sup>^{\</sup>star})$  The bits remain set until reset with RES\_SET (bit 6  $\it control\ word$  ).

# CCTRL\_I Control word

| Bit      | Name            | Function                             |

|----------|-----------------|--------------------------------------|

| 0        | CTRL_SYNC_SET   | activates the reset mode             |

| 1        | CTRL_DO_SET     | enables the digital output           |

| 2        | SW GATE SET     | sets the software gate               |

| 3<br>4   | -               | reserved                             |

| 5        | COUNTERVAL_SET  | sets counter temporarily             |

|          |                 | to the value of set value            |

| 6        | RES_SET         | resets the bits                      |

|          |                 | STS_CMP, STS_END, STS_OFLW, STS_UFLW |

|          |                 | and STS_ZP with edge 0-1             |

| 7        | -               | reserved                             |

| 8        | CTRL_SYNC_RESET | deactivates the reset mode           |

| 9        | CTRL_DO_RESET   | disables the digital output          |

| 10       | SW_GATE_RESET   | resets the software gate             |

| 11<br>15 | -               | reserved                             |

Fast introduction

#### **Parameters**

DS - Record set for access via CPU, PROFIBUS and PROFINET

IX - Index for access via CANopen

SX - Subindex for access via EtherCAT with Index 3100h + EtherCAT-Slot

More can be found in the according manual of your bus coupler.

| Name                                                     | Bytes | Function                | Default | DS  | IX             | SX  |

|----------------------------------------------------------|-------|-------------------------|---------|-----|----------------|-----|

| DIAG_EN                                                  | 1     | Diagnostic interrupt*   | 00h     | 00h | 3100h          | 01h |

| CH0A                                                     | 1     | Input frequency track A | 02h     | 01h | 3101h          | 02h |

| CH1B                                                     | 1     | Input frequency track B | 02h     | 01h | 3102h          | 03h |

| CH2L                                                     | 1     | Input frequency Latch   | 02h     | 01h | 3103h          | 04h |

| CH3G                                                     | 1     | Input frequency Gate    | 02h     | 01h | 3104h          | 05h |

| CH4R                                                     | 1     | Input frequency Reset   | 02h     | 01h | 3105h          | 06h |

| CH5                                                      | 1     | 0 (fix)                 | 00h     | 01h | 3106h          | 07h |

| INT_I                                                    | 1     | Interrupt behavior*     | 80h     | 80h | 3107h          | 08h |

| FCT_I                                                    | 1     | Counter function*       | 40h     | 80h | 3108h          | 09h |

| MODE2_I                                                  | 1     | Counter mode 2*         | 00h     | 80h | 3109h          | 0Ah |

| MODE3_I                                                  | 1     | Counter mode 3*         | 00h     | 80h | 310Ah          | 0Bh |

| END_I                                                    | 4     | End value               | 00h     | 81h | 310Bh310<br>Eh | 0Ch |

| LOAD_I                                                   | 4     | Load value              | 00h     | 81h | 310Fh311<br>2h | 0Dh |

| HYST_I                                                   | 1     | Hysteresis              | 00h     | 81h | 3113h          | 0Eh |

| PULSE_I                                                  | 1     | Pulse                   | 00h     | 81h | 3114h          | 0Fh |

| *) This parameter may only be transferred at STOP state. |       |                         |         |     |                |     |

#### **Control counter**

The counter is controlled via the internal gate (I gate). The I gate is the sum of hardware (HW) and Software gate (SW), where the *HW* gate evaluation may be deactivated via the parameterization.

#### HW gate:

Open (activate):

edge 0-1 at the gate input of the module

Close (de-activate):

edge 1-0 at the gate input of the module

#### SW gate:

Open (activate):

in user program by edge 0-1 SW\_GATE\_SET in the control word

Close (deactivate):

in user program by edge 0-1 SW\_GATE\_RESET in the control word

In-/Output area > Input area 12byte

#### **Counter output**

The following behavior for the output channel may be set via the parameterization:

- No comparison: output is not influenced

- Counter value ≥ comparison value: output is set

- Counter value ≤ comparison value: output is set

- Counter value = comparison value: output is set

Please consider that the output may only be controlled, when the bit STS\_CTRL\_DO in the *counter status* is set.

# 4.2 In-/Output area

# 4.2.1 Input area 12byte

#### Input area

At CPU, PROFIBUS and PROFINET the input area is embedded to the corresponding address area.

IX - Index for access via CANopen

SX - Subindex for access via EtherCAT with Index 6000h + EtherCAT-Slot

More can be found in the according manual of your bus coupler.

#### 12byte

| Addr. | Name   | Bytes | Function       | IX    | SX  |

|-------|--------|-------|----------------|-------|-----|

| +0    | CV_I   | 4     | Counter value  | 5400h | 01h |

| +4    | CL_I   | 4     | Latch value    | 5401h | 02h |

| +8    | CSTS_I | 2     | Counter status | 5402h | 03h |

| +10   | C_US   | 2     | μs ticker      | 5403h | 04h |

# CV\_I Counter value

The counter value always contains the current value of the counter.

#### CL\_I Latch value

With an edge 0-1 at the Latch input the recent counter value is stored at Latch value.

#### CSTS\_I Counter status

| Bit | Name        | Function                           |

|-----|-------------|------------------------------------|

| 0   | STS_SYNC    | Reset was active                   |

| 1   | STS_CTRL_DO | Is set                             |

|     |             | when digital output is enabled     |

| 2   | STS_SW-GATE | Status software gate               |

|     |             | (set when SW gate is active)       |

| 3   | STS_RST     | Status reset input                 |

| 4   | STS_STRT    | Status hardware gate               |

|     |             | (set when HW gate is active)       |

| 5   | STS_GATE    | Status internal gate               |

|     |             | (set when internal gate active)    |

| 6   | STS_DO      | Status digital counter output (DO) |

In-/Output area > Output area 10byte

| Bit            | Name                               | Function                                      |

|----------------|------------------------------------|-----------------------------------------------|

| 7              | STS_C_DN                           | Status set                                    |

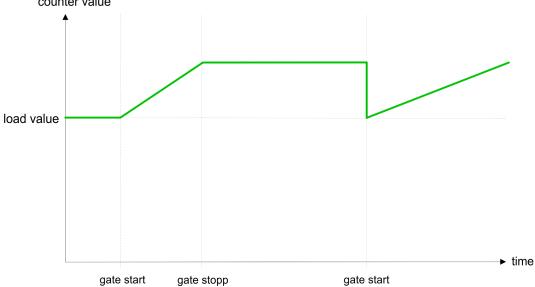

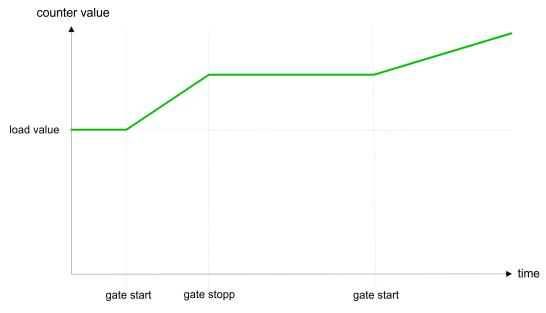

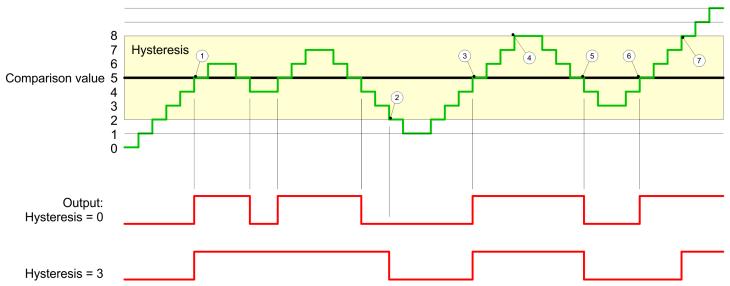

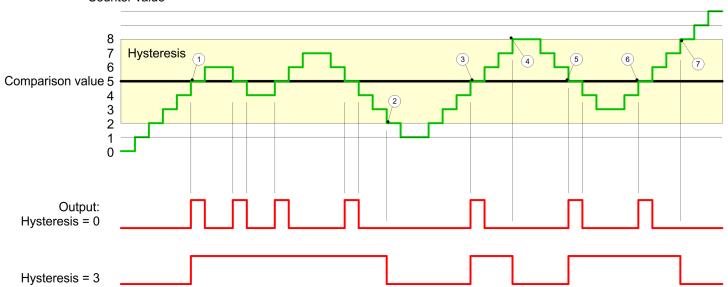

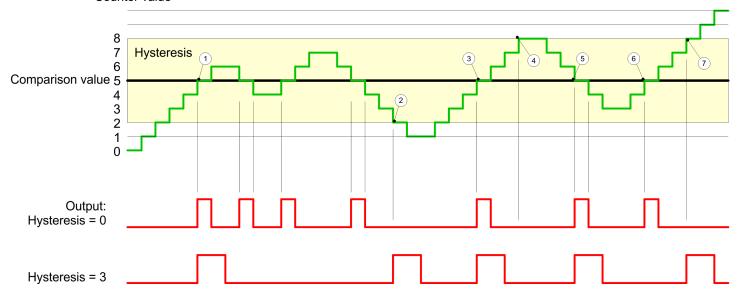

|                |                                    | at counter direction backward                 |